此文档主要记录本人在PCB硬件设计上的所有经验技术总结

1.

2.常用布线技巧(无顺序,想到哪写哪)

2.1 关于扇出

扇出是为解决Layout中针对多引脚封装的布线繁杂问题。两层板设计一般一面横线,一面竖线,起码保证两扇出过孔间有能加入一条

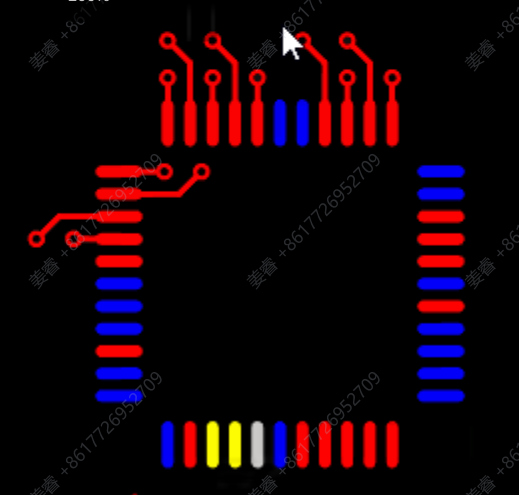

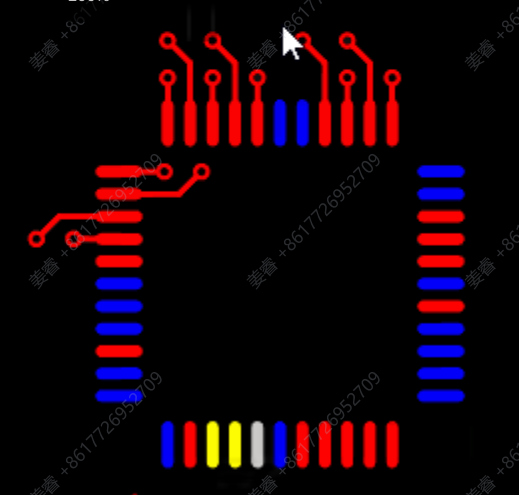

横线,以MCU为例,参考扇出如下图所示

2.常用Layout技巧(无顺序,想到哪写哪)

2.1 关于扇出

扇出是为解决Layout中针对多引脚封装的布线繁杂问题。两层板设计一般一面横线,一面竖线,起码保证两扇出过孔间有能加入一条横线,以MCU为例,参考扇出如下图所示 ,广义上的扇孔其实是针对一个模块把内部连接完成,把外部需要的线全部打孔占位。

,广义上的扇孔其实是针对一个模块把内部连接完成,把外部需要的线全部打孔占位。

9e8ffe6 (更新)

2.2 关于拉线

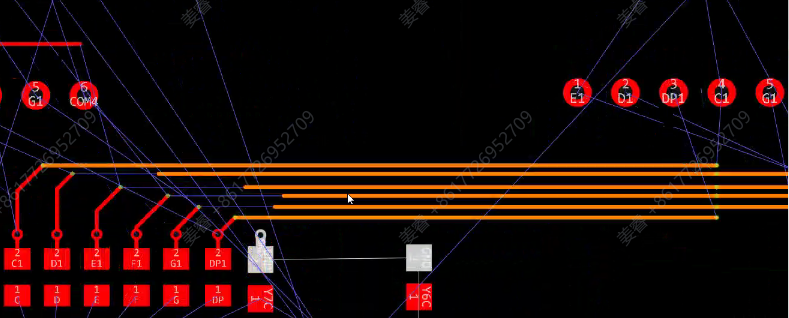

拉线为保证连线更加美观,将元件的所有引脚聚成一股拉出,减小漏连概率且提高观赏性,参考拉线如下图所示

2.3 尖角铜及处理方法

尖角铜指铺铜时由于结构原因,区域限制导致铺铜出现宽高比非常小的部分,该部分在实际电路运行时往往会导致电信号回流,对板结

构产生较大影响!,实际设计中需要予以避免消除。

解决思路:能打地孔则打孔,无法打孔则设置禁止区域重新铺铜。

2.4 定位孔

=======

尖角铜指铺铜时由于结构原因,区域限制导致铺铜出现宽高比非常小的部分,该部分在实际电路运行时往往会导致电信号回流,对板结构产生较大影响!,实际设计中需要予以避免消除。

解决思路:能打地孔则打孔,无法打孔则设置禁止区域重新铺铜。

2.4 定位孔

9e8ffe6 (更新)

定位孔一般在附近增加1mm来设置禁止区域,防止由于定位元件(螺钉)导致的短接。

2.5 常用禁止铺铜走线元件

继电器、晶振(干扰严重)

继电器

小封装电阻电容内部禁止穿线

电感:电感器件下方尽量避免走线,同时所在层需要挖空铜皮处理,如果电感附近有走线,需要对信号线包地处理。

晶振:为时钟提供基准信号,决定电路的稳定性,布线时严禁在晶振中横穿其他信号线,同时尽量避免在晶振下方或附近布置高速信号线或电源线。同时应使用差分走线方式,并在晶振周围进行包地线处理(法拉第笼增强抗干扰),并且在晶振背面进行完整地平面铺设。

蓝牙模块:蓝牙模块在 PCB 设计时,在 PCB 布局布线空间充足的情况下建议设计模块内区域保持禁空,不进行信号布线且不进行布局其它器件在模块区域内部。

2.6 关于过孔

如果空间足够,尽量避免过孔直接打到焊盘上(美观加上可能会有焊料损失,焊接不牢固)

过孔,仅仅只是在顶层连接,且内层底层之间没有进行任何连接,即为天线过孔,天线过孔同样是会形成天线效应,会接受其他的信号干扰源。

2.7 关于线路加宽处理

电机电路驱动线要进行加宽处理,保证电机驱动功能正常。

喇叭功放,正负极线需要进行加宽处理,确保音频电路功能正常。

3.电源模块设计

一般常用PCB常用电源模块有LDO,开关电源和PMU电源,因此主要针对这三种模块进行设计规范。

3.1 LDO模块设计规范

以LDO核心元器件布局。

滤波电容按照先大后小原则,尽量靠近芯片引脚摆放。

电源输入输出端尽量远离,避免噪声耦合。

主干道处理,以铺铜代替布线。

3.2 开关电源模块设计规范

如果有Datasheet,以其推荐原理图设计布局,注意回流路径越短越好。

与LDO滤波电容摆放需求相同

使相邻电感垂直放置,大电感和大电容尽量布置在主器件面。

尽量保持单点接地,于主器件下方回流至地,避免开关噪声沿地平面传播。

开关电源模块内部信号互联线尽量短而粗,原理干扰源。

中间散热焊盘建议双面开窗

3.3 PMU模块设计规范

以PMU为中心,先考虑DC-DC(参考3.2),再考虑LDO布局(参考3.1)。

BUCK部分需要输入输出电容就近可靠接地,接地点靠近,做到回路尽可能短。

PMU的I2C走线尽量避免同层或者隔层的干扰

3.4 电源完整性分析

元件面、焊接面为完整的地平面。

关键信号与地层相邻,不跨分割,如不可避免,要适当加跨接电容

形成信号回流通道。优先电源平面和地平面紧耦合。

关键电源有一对应地平面相邻。

对于PCB上小范围内用到的电源如某个IC芯片的核心工作电压,尽

量在信号层上灌铜解决。平面的分割宽度20~30mil。对于模拟电源和数字电源的分割宽度需

适当加大,以防止数字电源对模拟电源的噪声干扰;压差大的电源

也需要增加。电源平面分割要尽量保持规则,不允许有细长条及哑铃形分割;注意电

源瓶颈的出现。相邻层不同的电源平面要避免交叠放置,以防止噪声的互扰。

模拟电源和模拟地;数字电源和数字地,在平面层分割时要严格分开,

不要在平面上存在容性耦合。电源的分割区域要正确,模拟电源区域上要避免有数字信号和数字器件,

数字电源区域上要避免有模拟信号和模拟器件,以防止噪声的互扰。电源层要比地层内缩1mm,并在内缩区域每隔150mil打屏蔽地过孔。

3.5 通用电源布局思路

输入端电源建议大面积两面同时铺铜处理

4.USB接口设计规范

4.1USB布局要点

接口靠近板边放置,方便拔插;

ESD器件靠近接口放置,走线需先经过ESD器件(ESD器件是防浪涌 与稳压管不同 原理图看着很像 注意区分)

在元件布局时,使差分线路最短,以缩短差分线走线距离。

EMI滤波器或共模电感需靠近USB插座放置,防止电磁辐射;

USB2.0接口需注意2.2ohm电阻, USB3.0接口TX N/P需要注意AC耦合电容布局,都需要靠近接口摆放;

阻抗要求控制:USB差分阻抗Zdiff为90Ω(常规差分阻抗一般为100Ohm、差分地过孔回流);

USB差分需要进行打孔包地,差分换层处需要打屏蔽地过孔。

差分需要进行对内等长,误差为±5mil;

如若在设计中有使用保护地,保护地的线宽>=100mil保护地和信号地之间的间距>=40mil;

USB3.0以上所有信号都需要进行对间等长(对间指不同的差分信号间);

USB3.0 SSTX N/P,RX N/P,换孔尽量不要超过2个,信号完整的参考平面,信号不能进行跨分割(跨分割:从另一个层面相对不同的完整参考平面跨过去了 会导致信号没办法做信号阻抗

事实上无法做所有信号线跨分割 所以只需要针对所有的等长信号不要跨分割即可);

5.存储器模块PCB设计

5.1 SDRAM布局布线要点

- 位置要求

靠近CPU或BGA放置

2片时,相对于CPU严格对称

空间足够时,与CPU放在同一面,空间不足时SDRAM顶底对贴

SDRAM到CPU推荐的中心距离:

中间无排阻时,900-1000mil

中间有排阻时,1000-1300mil - 端源匹配电阻应靠近输出管脚放置

- 拓扑结构: SDRAM的数据、地址线推荐采用菊花链布线和远端分支方式布线

- 始终处理: 对于时钟信号采用RCR滤波,包地或至少保证3W间距

- 电源处理: 首先也好保证SDRAM器件所有管脚靠近放置退耦电容

- 阻抗控制: 所有信号线控制50ohm

- 网络分组: 1.数据线每9根要求同组同层

2.地址线、时钟线、控制线分一组

3.所有电源和地分一组 - 所有信号线的间距满足3W原则

- 空间允许下,应该在数据线,地址线,时钟线之间加地线进行隔离,并放置地过孔

- 分组等长,误差100mil以内。

5.2 FLASH模块设计

- 靠近主控摆放

- 管脚滤波就近放置

- 串接电阻靠近主控摆放,串阻和主控布线长度≤300mil

- Flash和SDRAM公用信号时,布局采用菊花链

- 时钟包地处理